Last time I started designing a chord arpeggiator. We got as far as and articulating the specifications and then drawing a state machine to handle note transitions. Today we’ll try to minimize the gate count for transitioning between states and then simulate the logic using VHDL.

Logic Minimization

I decided to use Karnaugh Maps because I actually remember how to use them, and with only 8 variables the problem is still simple enough so that real logic minimization tools aren’t necessary yet. But ‘Aha!’ you say you have 10 variables 6 states and 4 inputs. Well since only one state can be active at a time the corresponding up and down states can be combined when working out the logic. To reduce typing I After working through the Karnaugh Map for each state I got this

- States

- Fundamental

- Third

- Fifth

- Seventh

- Fifth_down

- Third_down

- Inputs

- Third_on

- Fifth_on

- Seventh_on

- Decending_on

- Logic

- Fundamental = (not Third_on and not Fifth_on and not Seventh_on ) or (Third and not Fifth_on and not Seventh_on ) or ( Fifth and not Seventh_on and not Decending_on ) or ( Seventh and not Decending_on ) or ( Seventh and Decending_on and not Third_on and not Fifth_on ) or ( Fifth_down and not Third_on and Decending_on ) or ( Third_down and Decending_on )

- Third = ( Fundamental and Third_on )

- Fifth = ( Fundamental and not Third_on and Fifth_on ) or ( Third and Fifth_on )

- Seventh = ( Fifth and Seventh_on ) or ( Third and not Fifth_on and Seventh_on ) or ( Fundamental and not Third_on and not Fifth_on and Seventh_on )

- Fifth_down = ( Seventh and Fifth_on and Decending_on )

- Third_down = ( Seventh and Third_on and not Fifth_on and Decending_on ) or ( Fifth_down and Third_on and Decending_on)

if I was actually good at digital design I’d be able to simplify that down to something ridiculous like 3 NAND and 2 XOR gates. But I’m not and that is a lot of logic which means there’s probably some errors in it and we should do a simulation.

Simulation

For simulating this type of glue logic I like to write a program for an FPGA and see how it runs. Of course I don’t have an actual FPGA or FPGA programming tool since they’re pretty spendy. So, I use the next best thing a web base FPGA simulator called EDA Playground because it’s free and easy to use. There are a variety of FPGA programming languages to choose from on EDA Playground. I picked VHDL because I remember how to use it the best of the available languages.

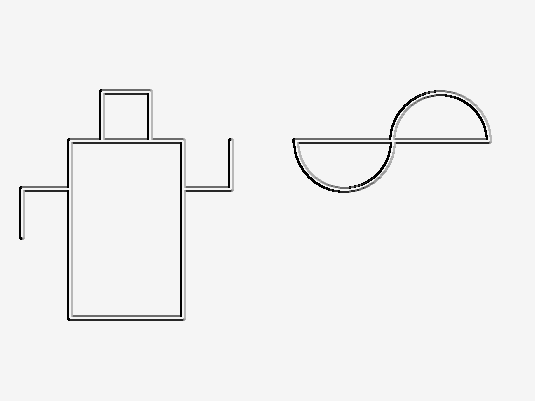

Link to EDA Playground arpeggiator simulation. While not my finest code it does show that the logic works. And EDA Playground provides a nice timing diagram for visualization.

Now that the logic is validated join me next time when we look at what the physical implementation of this thing will look like.