The next module I’m designing is an envelope generator. Since, I’m doing this while I wait for boards and part for other modules, I’ve decided to do a better job documenting the early part of the deign; so, if this project gets shelved for a bit I can spend less time remembering where the design is at. Now on to the fun bits.

What is an Envelope Generator

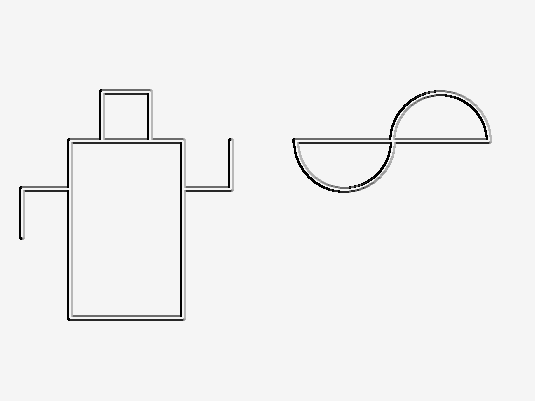

In signals an envelope describes how the signal changes in time. Since I’m primarily working with synths, the signal is going to be sound. To make a synth envelope an envelope generator outputs a sequence of voltages that are typically used as control voltages for an amplifier or filter. For example an envelope (blue) is used to control the amplitude of a sine wave (pink) using a voltage controlled amplifier.

A Block Diagram

How do we create a sequence of voltages? To start with lets put together a block diagram for a four part envelope generator commonly referred to as an ADSR (attack, decay, sustain, release).

I’ve expanded the A block to show likely sub-blocks the DSR blocks will contain similar sub-blocks. Working our way through the blocks. The inputs to the A stage, CV and control knob voltages, will be combined (probably added). The mixed control voltages will be fed to the driver block, where the control voltages will be interpreted into a signal to send to the memory block. The mixed control voltages will also be fed into a timer. When triggered the timer will close the switch between the driver and the memory block for a length of time determined by the control voltage. When the timer runs out the switch will open and the timer will signal that it is done to the control logic. On receiving a gate or trigger the control logic will trigger the timer connecting the stages driver to the modules memory block. When the control logic receives a ‘done’ signal from the timer in the current stage it will trigger the timer for the next stage. Articulating all of that makes me think about how easy it would be to do all of this with a micro controller. Which leads neatly into,

Constrains

- Eurorack module -> size – power – jacks

- Analog and glue logic components, no micro or purpose built ADSR chips

- Needs to utilize CV

- Only AR for first revision

- Attack peaks at 5 V

If I was sane I would uses a custom made ADSR chip or a microcontroller to build this modules. However I’m a little deranged so for the paper design I’ll be sticking with analog and discrete logic components. If I discover that I’ll need an excessive number of logic chips I’ll probably redo the design with a micro controller before moving on to prototyping. Since I’m only mostly insane there will be some constraints to start decay and sustain stages will be dropped from the first version. And more than likely the peak attack value will be fixed at 5 V. Since the ADSR stages will have a lot of overlap I may revisit some of these choices after I do the component level design for the attack stage. And lastly this is nominally going to be a Eurorack module so I’ll be working inside that voltage and size restrictions as well. Also since this isn’t going to be part of a standalone synth it’ll use CV in addition to potentiometers to determine timing parameters.

Design Outline

Now the blocks can be roughed in. No math yet just picking out common design patterns to fill in the blocks, get an idea of component count that sort of thing.

Memory and Buffer

Were going to start with the easy sections first. For memory the classical analog memory element, a capacitor, seem like an appropriate starting point. and the buffer will be a high input impedance op-amp connected as a voltage follower.

The astute among you will note that this is the ‘hold’ part of a sample and hold circuit, and I mentioned using a switch as part of the driver circuit which would be the ‘sample’ part. Whether this sample and hold will be implemented as discrete components or using a dedicated sample and hold IC will be determined later. Since the capacitor has four potential input ‘signals’ to sample from likely discrete components will be used.

Driver

As the memory component is a capacitor, a reasonable first choice for the driver is a current source (sink for D and R blocks). Right now the switch can be penciled in as an NMOSFET, but switching could be implemented by turning the current source off via the OpAmp inputs. Adding a current limiting resistor between the transistors will probably be a good idea as well.

Timer

The timer is going to need to generate a high voltage pulse to control the NMOSFET in the driver stage. A one shot is an option but a 555 timer comes with a handy control voltage (CV) input pin so that’ll be the starting point. When the ‘TR’ input is pulled low by the control logic the output, Q, will be driven high, and C will begin to charge. When the voltage on C exceeds the input control voltage the output will be driven low and the capacitor will be discharged through the DIS pin. So the values of R, C, and CV will determine on time. reset is penciled in to be always tied on however if the AR is retriggered before finishing ideally the entire process would start again from the beginning. So the reset pin may eventually be connected to the control logic.

Input and Input Mix

The final stage is the input mix. At least one op-amp will be needed to combine and buffer the inputs and adjust their range to match the input range of the driver and timer stages. A second op-amp is needed because the driver and timer stage need different control voltages to achieve the desired envelope shape. The op-amps as shown are connected in inverting configuration because it is anticipated that gains less than 1 will be required between the input and the output of the mix. however both driver and current stages as shown require positive input voltages so a third op-amp may be required. We’ll find out more once all of the math is done.

Everything so far

This is the design so far. I’ve added in a connection for output feedback to the input. Feedback control is almost always beneficial. Although until more of the design is fleshed out it’s not clear if the feedback will be more appropriate at the input or somewhere in the middle.

Next time we’ll do some math or think about the control logic or maybe both.