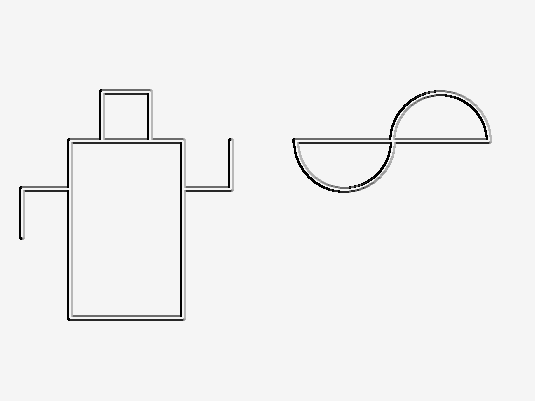

A few days ago I came across the circuit diagram for the ADSR in the ARP 2600. After I got done being amazed at how the designers accomplished so much with just a handful of transistors, I learned a couple of things to bring back to my A(DS)R design. First a simplified version of the ARP 2600 ADSR schematic.

What’s been simplified? A substantial amount of circuitry has been replaced with ‘black (blue) boxes’ Their functionality is their outputs latch high (1) on event detection and reset low (0) some time after the gate signal falls to 0 (actual operation is more nuanced, but this description is sufficient for this discussion). Next, there are no actual logic gates in the original circuit; however, parts of the circuit function in a similar manner to logic gates. So these have been substituted. Finally, a number of ‘voltage controlled switches’ have been added. These are all transistors in the actual design. However, they are all different types of transistors (NJFET, PJFET, PNP) with different operating modes, and I wanted them all to have the same conceptual functionality for the sake of discussion. So they’ve all be replaced. The ‘voltage controlled switches function as follows a high control voltage closes the switch and a low control voltage opens the switch. (so they’re non latching relays).

Operation

Initial state

Prior to receiving a gate input the Release Switch is closed and the Memory Capacitor is drained to 0 V. The Sustain value is set via the npn transistor charging the Sustain Capacitor in the bottom right.

Gate Rising Edge

When the Gate signal goes high the release switch opens, and the rising edge control is set high. Since the other two detection blocks are still low the Attack Switch closes starting the note.

Gate on Attack ending

The Attack ends when the Memory Capacitor is charged to it’s maximum value somewhere between 8-10 V. The max value detection block is set high turning off the Attack Switch and turning on the Decay-Sustain Switch. Once the Decay-Sustain Switch is closed the Memory Capacitor drains through the Decay control until it reaches the same voltage as the Sustain Capacitor. Elegantly simple.

Gate Falling Edge

The last stage is the falling edge of the gate. The falling edge detection block is set high and the Decay-Sustain Switch is opened. Once the gate has transitioned to 0 V the Release Switch is closed, and the Memory Capacitor is drained through the Release Control. Once the Memory Capacitor is drained the cycle is read to begin again.

Take Aways

My first note is that a capacitor is used as the voltage value storage device, and there’s an op-amp buffer between the capacitor and the output. That’s exactly the configuration I chose. What a coincidence! Great minds think alike. Or there’s really only one device capable of storing analog voltages and that storage mechanism requires a high input impedance to low output impedance buffer to be useful to subsequent modules. Who knows?

The next note is that there is nothing resembling a timer anywhere in this. All transitions happen because of event detection and feedback. So I’m going to drop the timer from my design, and just use feedback. I might add it back in as part of the ‘trigger function’ but we’ll have to get further along in the design to see.

The last note is the simplicity of the Decay-Sustain portion of the circuit. I was originally thinking that I’d need two switches and a current source tuned to the the natural losses of the ‘memory’ capacitor for the Sustain. I was also anticipating needing a fair amount of components to control the transitions between the states. Now I’m thinking of doing a paper design for a voltage controlled Decay-Sustain in a similar vein to the this one to see how much complexity it would add.